Forum Romanians in Micro- and Nanoelectronics, 6 November 2018, Romanian Academy, Bucharest, Romania

# Systematic and optimized design of analog ICs

Marius Neag, Technical University, Cluj-Napoca, Romania

Revised version 06.12.2018

### Overview

- ➢ The "DERFAIC" Research Group

- Brief description

- Examples of ICs and modules developed by DERFAIC members

- Systematic and optimized design

- Main Approaches

- Design Example: standard OpAmp with Miller Rc-Cc frequency compensation

- Low Drop-Out Voltage Regulators (LDOs ) designed by PHD students

- Main design challenges

- Error amplifier

- Larger SR for faster transient response: Class-AB Recycling Folded Cascode OTAs

- Over-Current Protection

- Improved design by using Electro-Thermal simulations

- Over-Temperature Protection

- Design methodology based on Electro-Thermal simulations

- Design Example

- Summary and Conclusions

#### DERFAIC research group: Main areas of activity

- Design of RF, Analog and Mixed–Signal Integrated Circuits (ICs)

- Design and physical implementation of board-level modules with ICs

- Optimization techniques and tools for synthesis of analog and digital circuits

- Modelling and characterization of integrated circuits and systems

- Multifactor analysis of integrated circuits and systems, yield analysis

- High performance power management circuitry, including energy harvesting & conversion and wireless power transfer

- Electronic circuits and systems for acoustics: modelling the acoustic behavior of enclosures, optimized synthesis of acoustic equalizers

- Website: http://icdesign.utcluj.ro

# DERFAIC research group: Resources

#### Staff

- 8 academic staff members

- 10 PhD students

- 5 MSc and BSc students with scholarships

#### Funding sources

- research grants with public funding

- R&D services for companies within the semiconductor industry

#### Infrastructure

- 2 laboratories with dedicated computer network

- 2 laboratories with standard equipments **Technical support**

- Cadence Academic Network membership

- Access to state-of-the-art Cadence suites of IC design tools

- Access to technical support, courses and training sessions

- Europractice membership

• Access to 90nm, 0.15um and 0.18um CMOS based logic, RF/mixedsignal and high-voltage CMOS technologies

• Access to state-of-the-art manufacturing facilities for IC prototyping

Faculty-to-IC designer career path based on scholarships:

- Scholarships provided by DERFAIC for undergraduate students

- MSc grants provided by our industrial partners

Or

• MSc and PhD students funded through active involvement in research projects

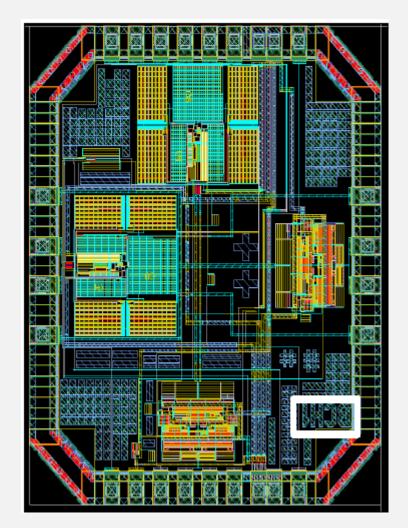

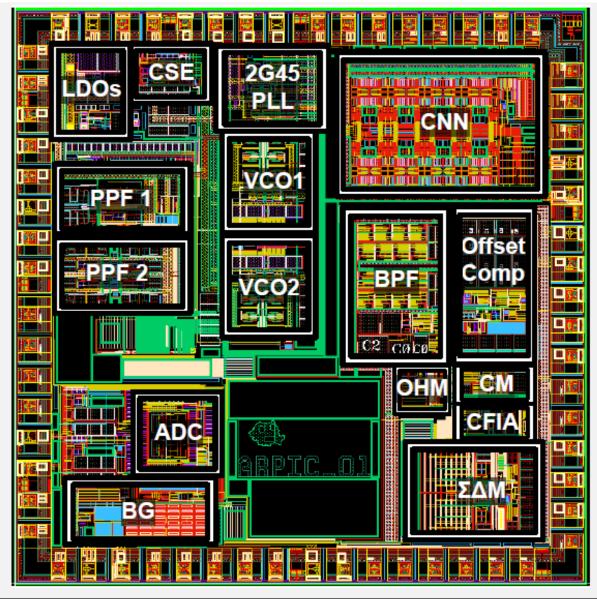

#### ARPIC\_01

#### ARPIC = Romanian Academic Platform for IC

**Development:** an open cooperation framework for joint development and silicon implementation of integrated circuits for teaching and academic research purposes **ARPIC01** = first modern analog IC designed exclusively by students and academics from three Romanian Technical Universities: Bucharest, Iasi and Cluj-Napoca

# Blocks developed by the DERFAIC = Nord-West corner of the chip :

- Frequency synthesizer, Fmax = 2.45GHz

- Rail-to-rail voltage controlled oscillators (VCOs)

- Polyphase filters for image rejection in low-IF integrated radio receivers

- Low dropout voltage regulators (LDOs) with and without external decoupling capacitors

- High precision bidirectional current sensor

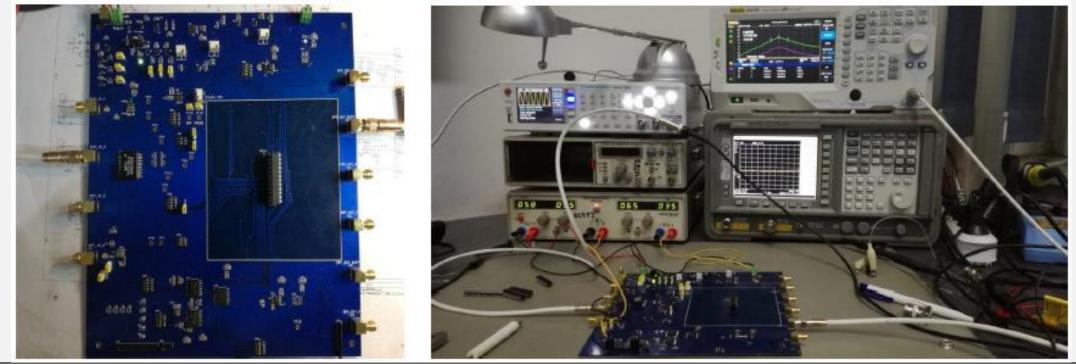

# Integrated circuit for automotive applications: analog front-end for Hall sensor

Aim: full design and characterization of an ASIC according to requirements set by the customer (a multinational IC design company, well known in automotive );

Main blocks: an instrument amplifier and a digitally-programmable bandpass filter. Two circuit implementations were completed for the instrument amplifier. Also included the usual auxiliary circuitry – bias, test, SPI. Main results:

- 1<sup>st</sup> silicon fully functional and met the specs

- Test board designed and populated

- Complete IC characterization, including sensitivity wrt noise

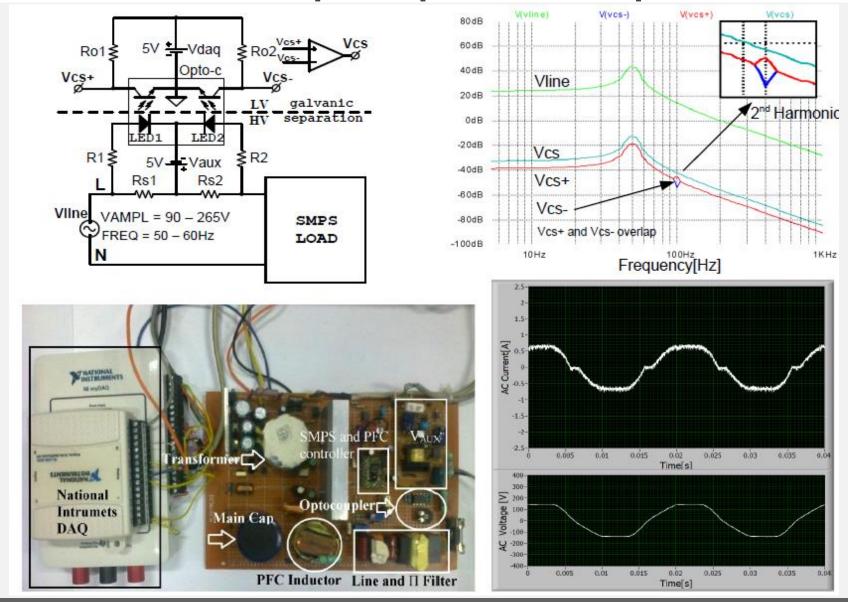

#### Current line sensor with matched optocouplers for active power factor correction

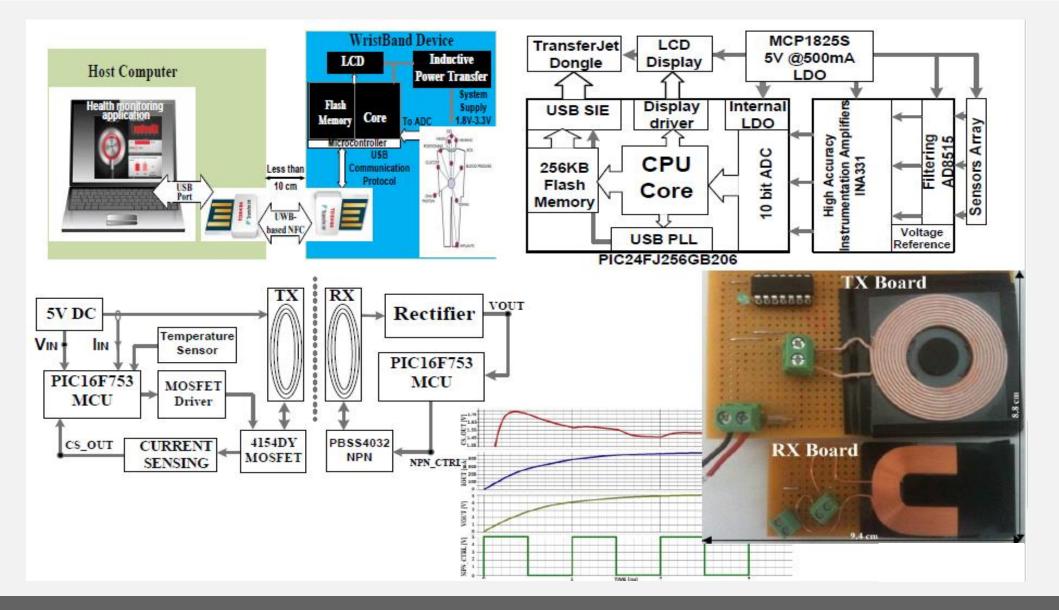

#### Wearable health monitor with NFC and inductive power transfer

Forum Romanians in Micro- and Nanoelectronics, 6 November 2018, Romanian Academy, Bucharest, Romania

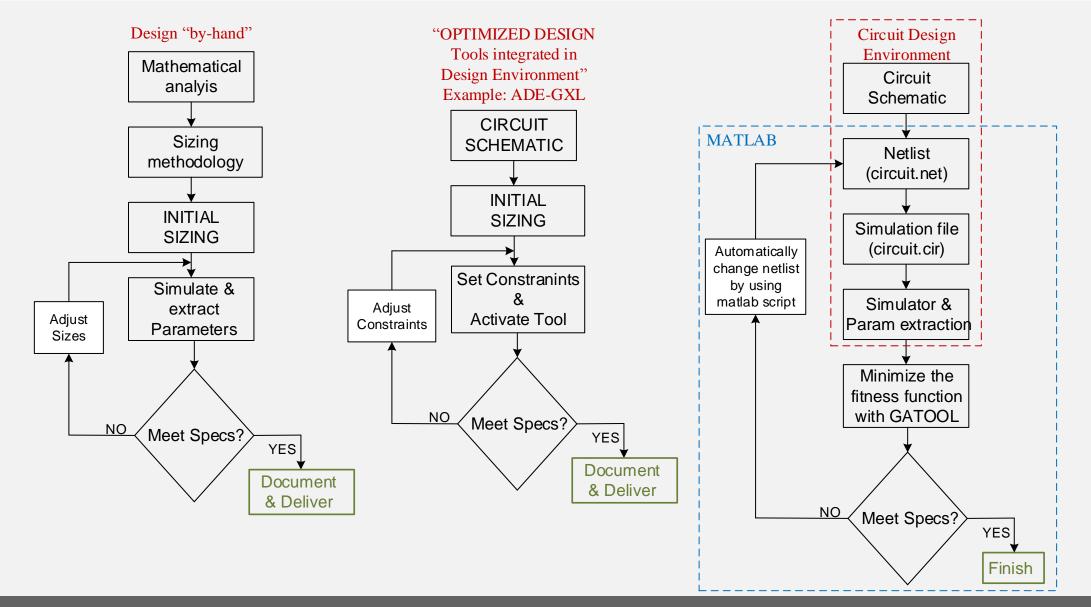

# Approaches to optimized design illustrated by a simple example: the

**Miller OpAmp**

# Approaches to systematic and optimized design/sizing

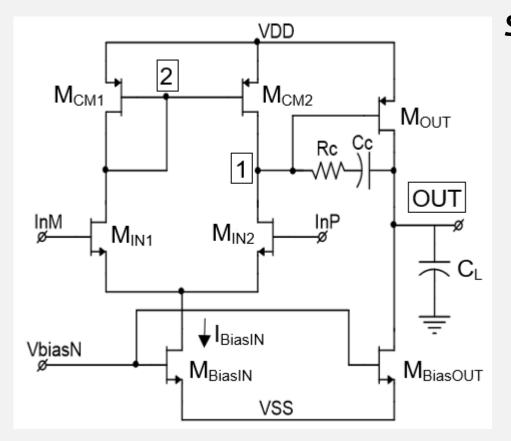

### Design Example: Standard Miller OpAmp with Rc-Cc compensation

#### Standard Miller OpAmp: Mathematical analysis

DC gain  $A_0 = G_{mIN}G_{mOUT}R_{o1}R_{oOUT}$  $= g_{mIN}g_{mOUT}(r_{DS_IN}||r_{DS_CM}) \cdot (r_{DS_OUT}||r_{DS_BiasOUT})$

Dominant pole & GBW

$$f_{pole1} \approx \frac{1}{2\pi R_{o1}R_{o0UT}g_{mOUT}C_c}; GBW = A_0 \cdot f_{pole1} = \frac{g_{mIN}}{2\pi C_c}$$

Main secondary pole and zero

$$f_{Pole2} = \frac{g_{mOUT}}{2\pi C_L}$$

$f_Z^{Rc} = -\frac{1}{2\pi (1/g_{mOUT} - R_c)C_c}$

Slew-Rate and max output voltage amplitude frequency

$$SR = \min(\frac{I_{BiasIN}}{C_c}; \frac{I_{BiasOUT}}{C_L + C_c}); f_{OUT\_max} \cdot V_{OUT_max} < \frac{SR}{2\pi}$$

Offset voltage at the OA input,  $V_{OS}$ , & condition to minimize it

$V_{OS} = f[V_{DSsatIN}, (W \cdot L)_{IN}, V_{DSsatCM}, (W \cdot L)_{CM}]; V_{DSsatCM} = V_{DSsatOUT}$

# Design Example: Standard Miller OpAmp with Rc-Cc compensation

#### Sizing Methodology

|                                                                                                                                                                                                                                                  |                                                                                                         | Specs                       | Sizing Equations                                                                                 |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| $C_{\rm C} = 0.22C_{\rm L}$                                                                                                                                                                                                                      | Start with same condition for Cc as the standard Cc-<br>only approach but use Rc-Cc comp network        |                             | $GBW = \frac{G_{m1}}{2\pi C_{c}} (1)$                                                            |  |  |  |  |

| $(1) \rightarrow g_{m1}$                                                                                                                                                                                                                         | Eq. 1 => The transconductance of the input<br>transistors gm1 obtained from GBW spec.                   | A <sub>0</sub><br>GBW       | $2\pi C_{\rm C}$ $V_{os} = F(v_{dsat1}, (WL)_1)  (2)$                                            |  |  |  |  |

| $(2) \rightarrow I_{D1,2}$                                                                                                                                                                                                                       | 1 <sup>st</sup> value for the input transistors bias current results from matching and linearity specs. | PM<br>SR                    | $SR = \frac{2I_{D}}{C_{C}}(3)$                                                                   |  |  |  |  |

| $(3) \rightarrow SR$                                                                                                                                                                                                                             | Verify that the resulting value for SR is equal (or larger) than the specified SR                       | I <sub>dd_max</sub>         | $f_{z} = \frac{1}{2\pi (1/G_{m2} - R_{c})C_{c}}$ (4)                                             |  |  |  |  |

| $I_{D6} = I_{dd_{max}} - 2 \cdot I_{D1}$                                                                                                                                                                                                         | ,2 The rest of the available (spec'ed) current is allocated to the second stage.                        | C <sub>L</sub> PM=<br>Noise | =90-arctg(GBW/f <sub>p2</sub> )-arctg(GBW/f <sub>z</sub> ) (5)<br>$gm = \frac{2I_{D}}{Vdsat}(6)$ |  |  |  |  |

| $Vdsat_6 \rightarrow Gm_2$                                                                                                                                                                                                                       | Based on Gm/Id curves determine the optimum<br>Vdsat for maximum Gm2; check linearity                   | V <sub>dsat_MIN</sub>       |                                                                                                  |  |  |  |  |

| $(4,5) \rightarrow PM \rightarrow R_C$                                                                                                                                                                                                           | Calculate Rc considering the expressions (4)<br>and (5) for fz and PM, respectively                     | $(W * L)_{MIN}$             | $r_{\rm DS} = \frac{V_{\rm E}L}{I_{\rm D}}(7)$                                                   |  |  |  |  |

| $\begin{array}{c} (6,7) \rightarrow A_0 \end{array} \qquad \begin{array}{c} \text{Calculate remaining Gm values using (6); then find optimal L and W} \\ \text{considering noise and matching requirements, as well as the DC gain} \end{array}$ |                                                                                                         |                             |                                                                                                  |  |  |  |  |

### Design Example for Miller OpAmp: Student versus Optimization tools

| Parameter                            | Specs  | Student<br>Design-by-hand<br>3 iterations | ADE-GXL,<br>Initial = "Min" | ADE-GXL,<br>Initial ="Student" | GA-based<br>Optimization |

|--------------------------------------|--------|-------------------------------------------|-----------------------------|--------------------------------|--------------------------|

| Idd_max [uA]<br>Vdd=1.2V             | < 1000 | 750                                       | 870                         | 940                            | 850                      |

| DC gain [dB]                         | 60     | 63.3                                      | 61                          | 62.7                           | 60.1                     |

| GBW [MHz]<br>Cload=1pF               | 500    | 510                                       | 517                         | 525                            | 502                      |

| PhaseMargin<br>[degrees]             | >60    | 61                                        | 61.5                        | 62.5                           | 60.1                     |

| GainMargin<br>[dB]                   | >10    | 21.6                                      | 17                          | 23.2                           | 16.5                     |

| SR [V/us]                            | 150    | 155                                       | 162                         | 175                            | 150                      |

| Ripple of<br>closed-loop<br>response | <1dB   | +0.7                                      | -3                          | +0.25                          | -0.9                     |

Forum Romanians in Micro- and Nanoelectronics, 6 November 2018, Romanian Academy, Bucharest, Romania

# Examples of systematic design: LDOs developed by PhD students

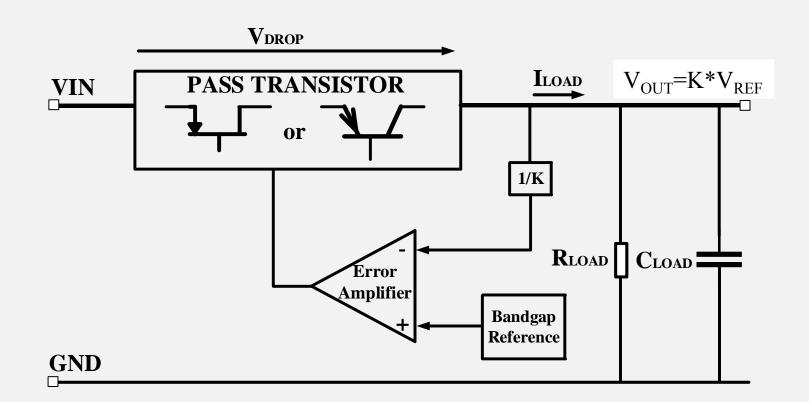

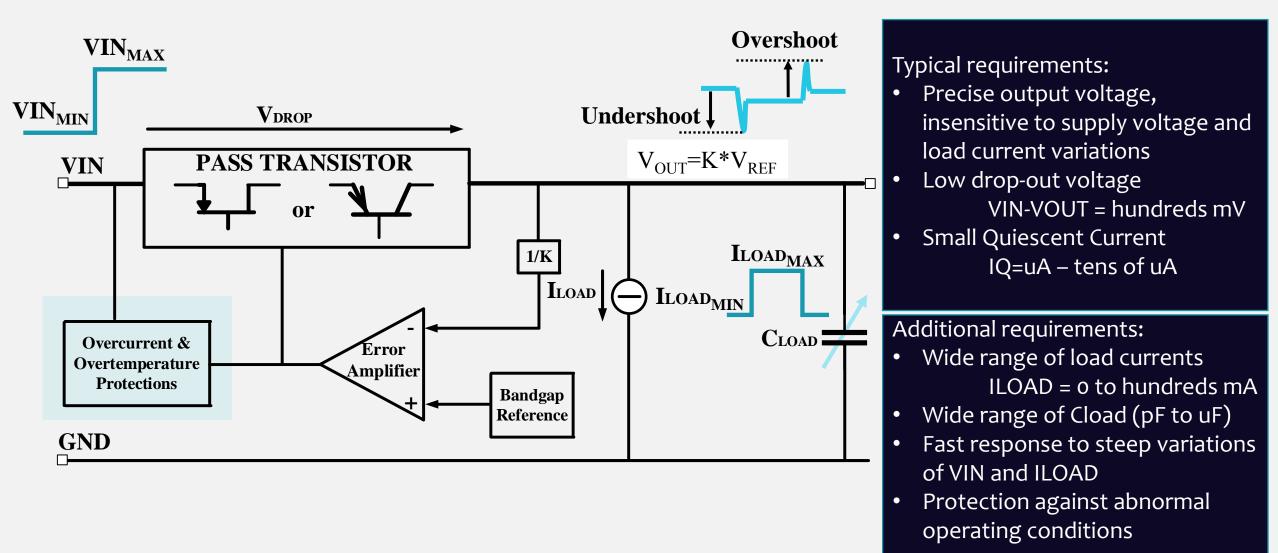

# LDO: brief description and typical requirements

Typical requirements:

- Precise output voltage, insensitive to supply voltage and load current variations

- Low drop-out voltage VIN-VOUT = hundreds mV

- Small Quiescent Current IQ=uA – tens of uA

# LDO: additional requirements and main design challenges

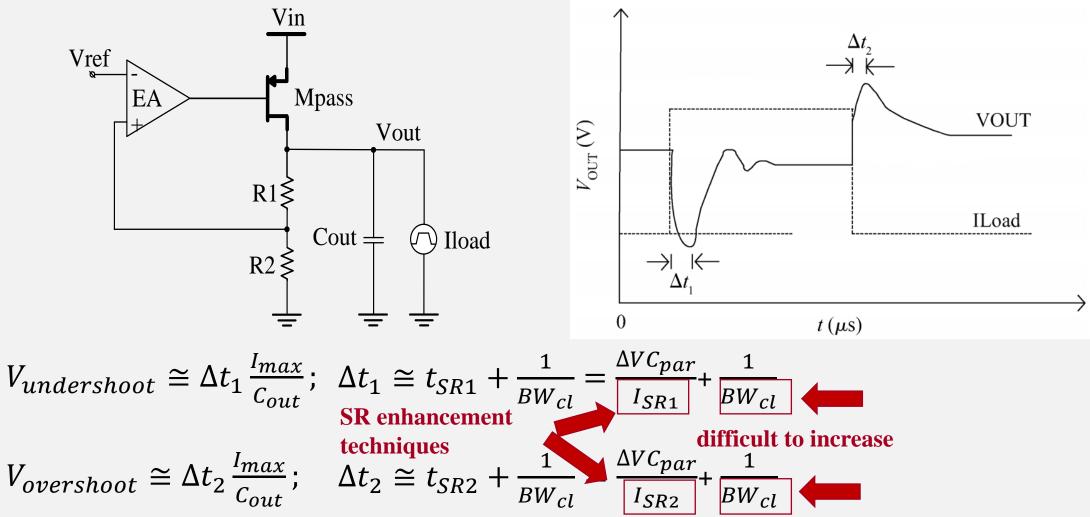

### Error Amplifier: Increasing SR for faster response to steep variations of I<sub>Load</sub>

Parameters that influence the load transient response of an LDO

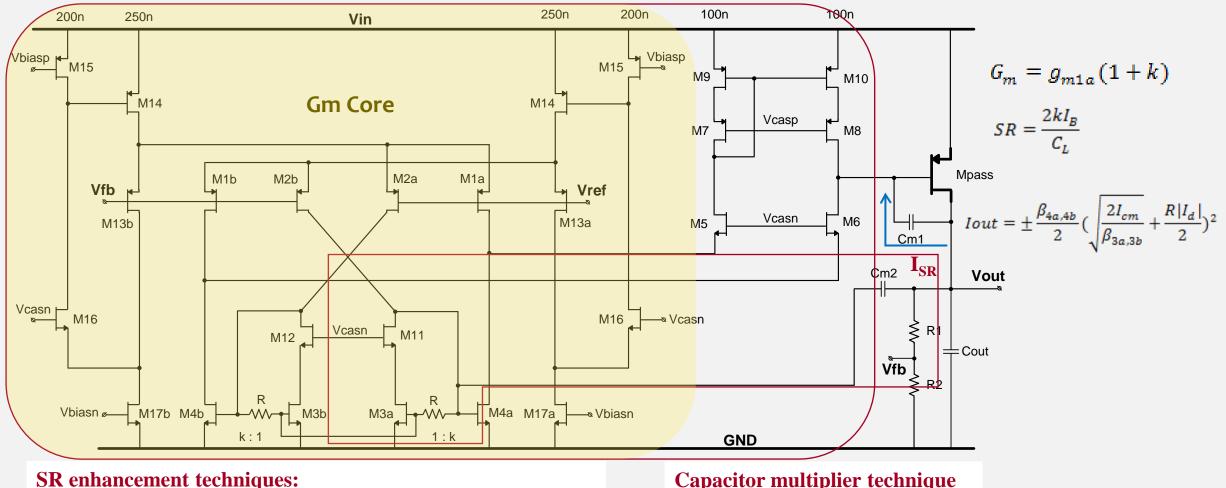

# Error Amplifier: Increasing SR for faster response to steep I<sub>Load</sub> variations

Super Class-AB Recycling Folded Cascode

- Current recycling

- Adaptive Biasing using cascoded Flipped Voltage Follower

Capacitor multiplier technique to create dominant pole

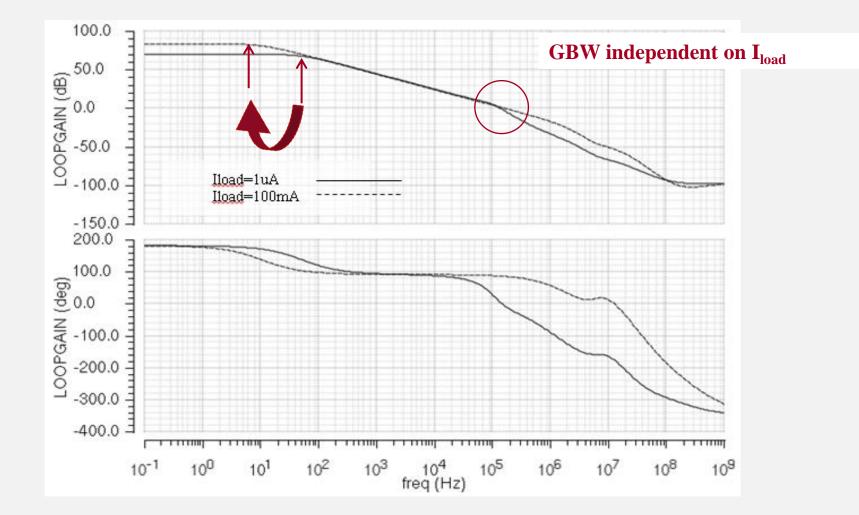

Small-signal analysis: Loop gain variation with I<sub>load</sub>

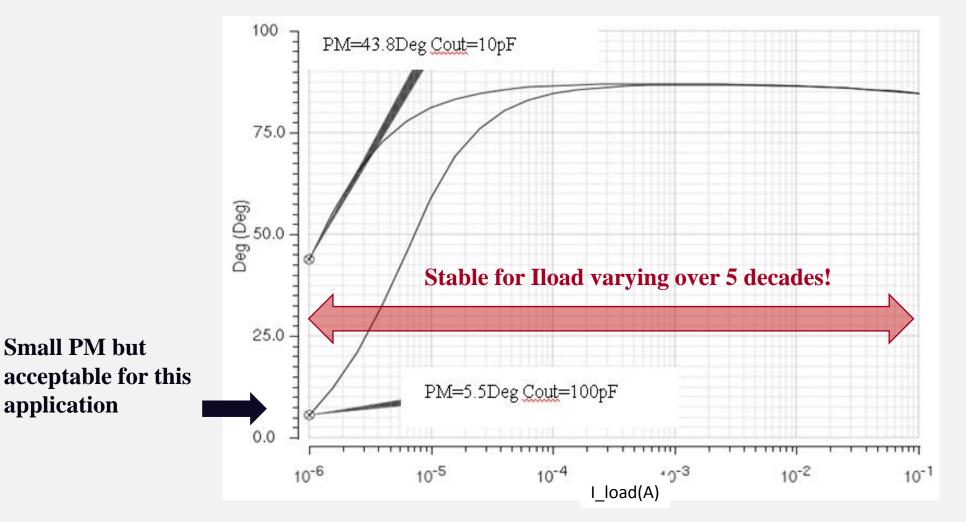

Small-signal analysis: PM variation with I<sub>load</sub>

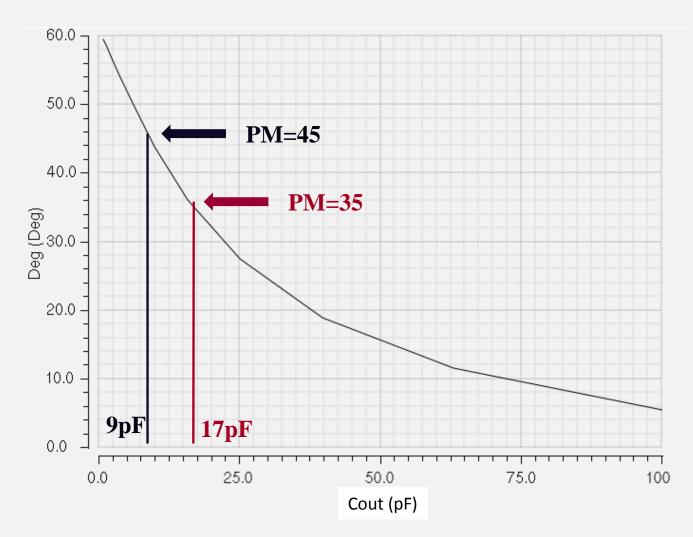

Small-signal analysis: PM variation with Cout @ small I<sub>load</sub>

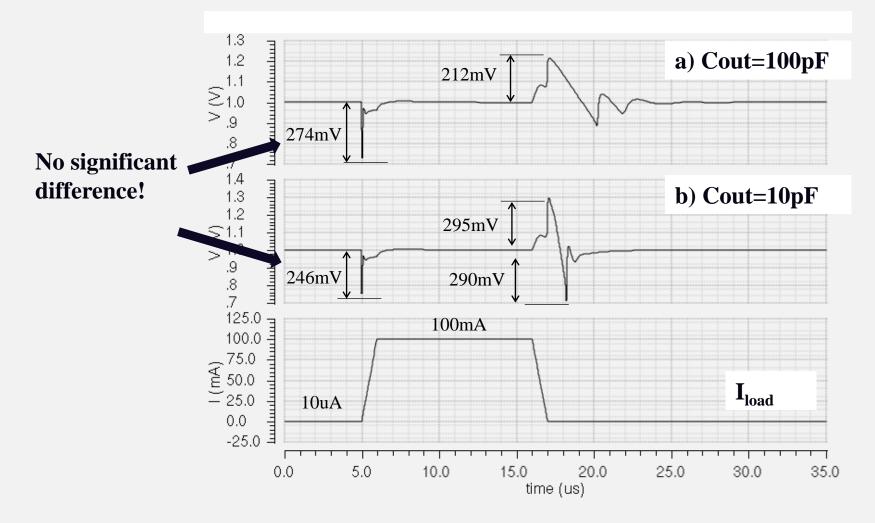

> Load transient response ( $I_{load}$  step from 10uA to 100mA,  $t_{rise} = t_{fall} = 1$ us):

# LDO: comparison between different topologies

| Parameter                                                                        | Wang -2010 | Saberkari – 2013 | Ming - 2012 | Recycled folded-<br>cascode CAS2015 |

|----------------------------------------------------------------------------------|------------|------------------|-------------|-------------------------------------|

| CMOS (µm)                                                                        | 0.35       | 0.18             | 0.35        | 0.18                                |

| Supply Voltage (V)                                                               | 4-6        | 1.2              | 2.5-4       | 1.8                                 |

| Output Voltage (V)                                                               | 2.5        | 1                | 2.35        | 1                                   |

| Dropout Voltage (mV)                                                             | 200        | 200              | 150         | 90                                  |

| lout (mA)                                                                        | 250        | 100              | 100         | 100                                 |

| Iq (μA)                                                                          | 20         | 3.7              | 7           | 1.12                                |

| Cout (pF)                                                                        | 100000     | 100              | 10-100      | 0-100                               |

| Response Time (ns)                                                               | N.A        | N.A.             | N.A         | 30                                  |

| ∆Vout (mV)                                                                       | 110        | 277              | 236         | 274                                 |

| Line regulation (mV/V)                                                           | 2          | N.A.             | 1           | 0.077                               |

| Load regulation (mV/mA)                                                          | 0.04       | N.A.             | 0.08        | 0.0028                              |

| FOM (fs) (Cout=100pF)<br>FOM = $\frac{\Delta V_{out}C_{out}I_q}{I_{out\ max}^2}$ | 3520       | 10.2             | 16.5        | 3.1                                 |

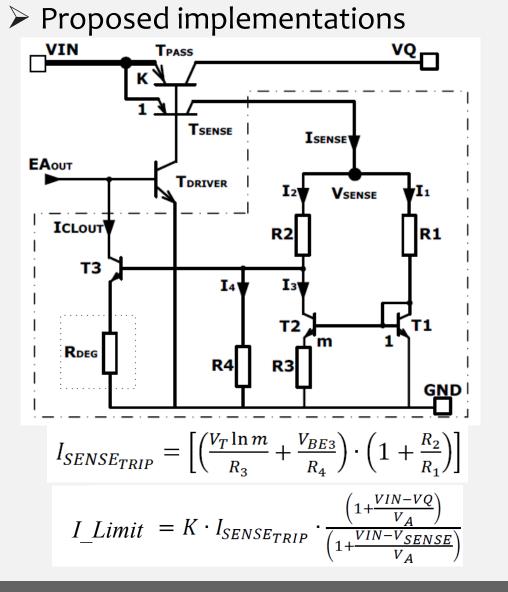

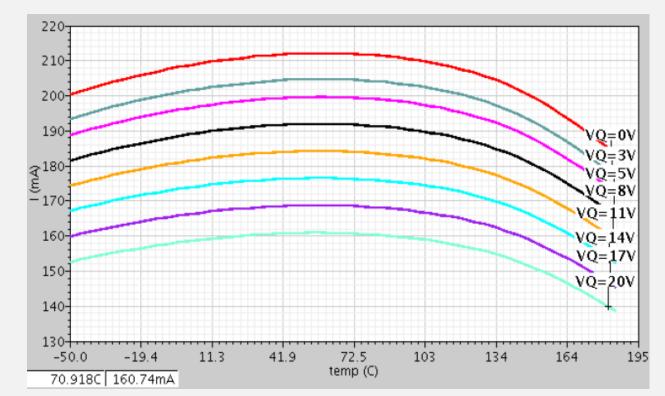

# Over-current protection

#### Simulations Results

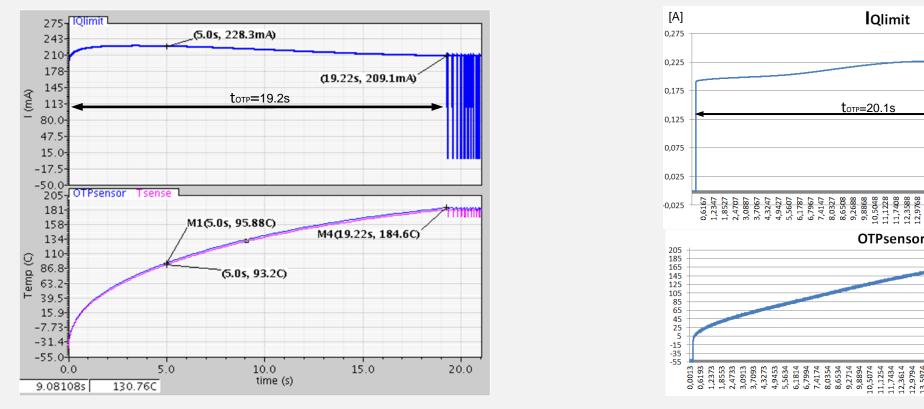

## Over-current protection: Electro-thermal simulations versus measurements

#### >Electro-thermal simulations results

#### >Measurements results

•IOlimi

> The maximum value of I\_Limit is almost the same for measurements and for the electro-thermal simulations, 223mA as against 228mA (both sims and measurements performed in the same scenario).

The dynamic behavior of the LDO is also in good agreement. The time until the over-temperature protection is activated (t  $\sim$ ) has a small variation of  $5^{\circ}$  between the measurements  $\rightarrow 20$  is and electric thermal simulations.

activated (t<sub>OTP</sub>) has a small variation, of 5% between the measurements – 20.1s and electro-thermal simulations – 19.2s

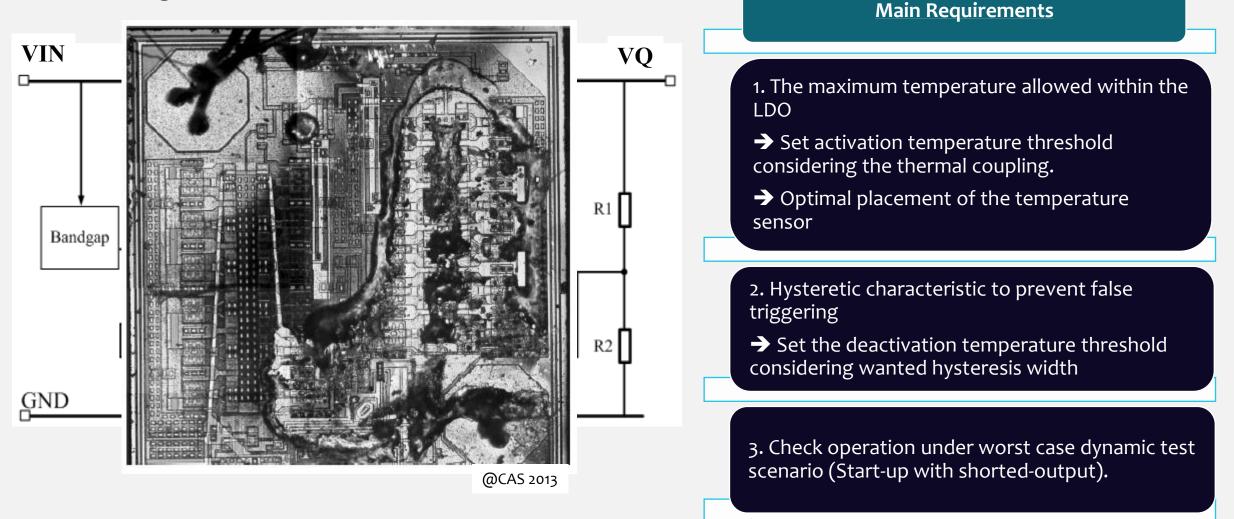

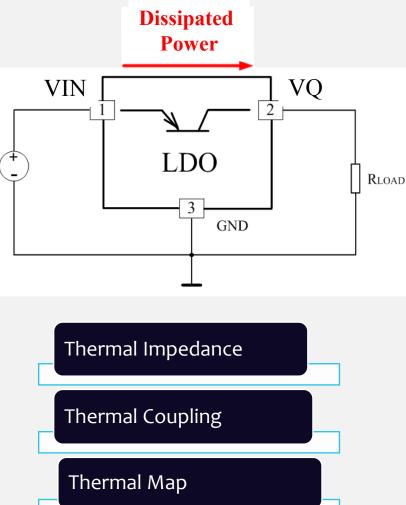

# Over-temperature protection: brief description and main requirements

Block Diagram

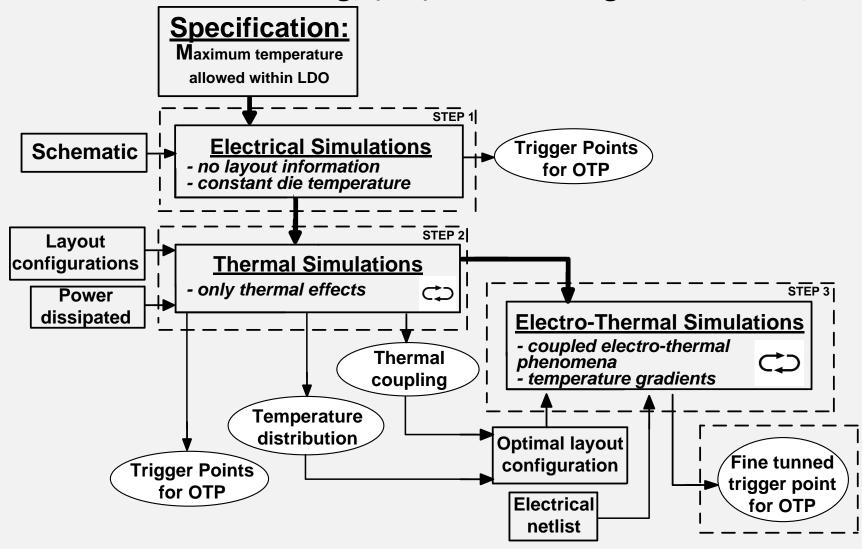

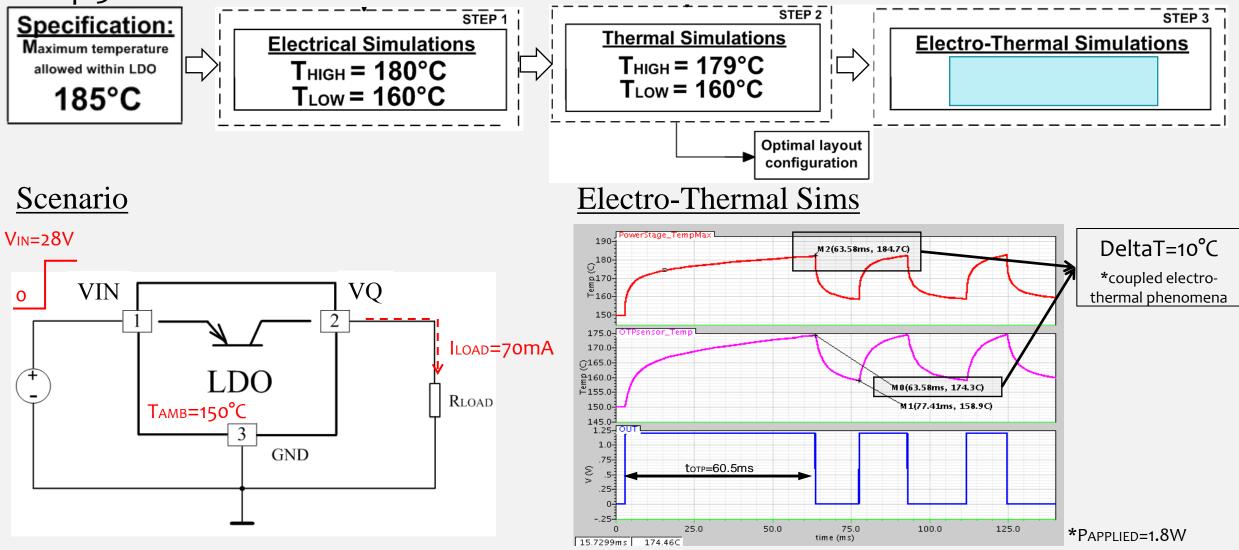

### Over-temperature protection: design based on electrical and thermal-only sims

#### ➤ Main ideas

#### Shortcomings

- The thermal-only simulations assume that the electrical parameters of the circuit do not change when the temperature varies due to the applied power

- Standard electrical-only simulations assume that all the devices within a chip operate at the same temperature

- The variation in time of the temperature distribution cannot be revealed by performing thermal only simulations – this could cause damage of the circuit

The dependency between the initial conditions (different scenarios regarding the polarization of the circuit) and the temperature distribution can be fully covered only by performing electro-thermal sims

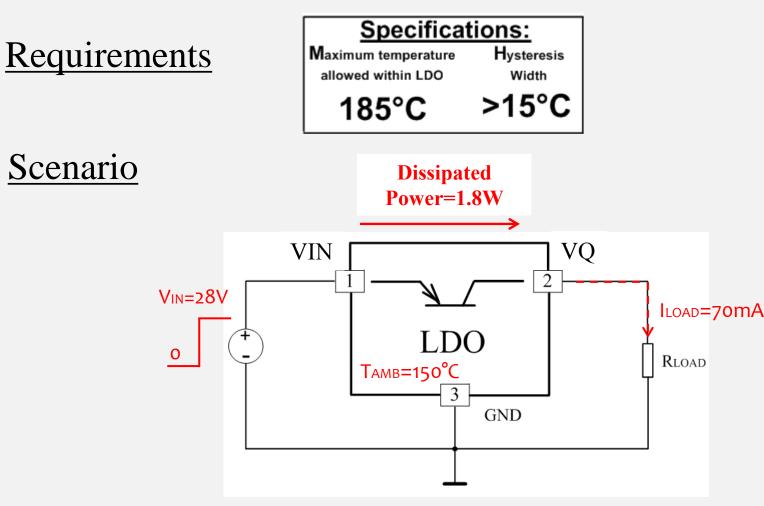

➢ Flow-chart of the methodology proposed to design OTP circuitry

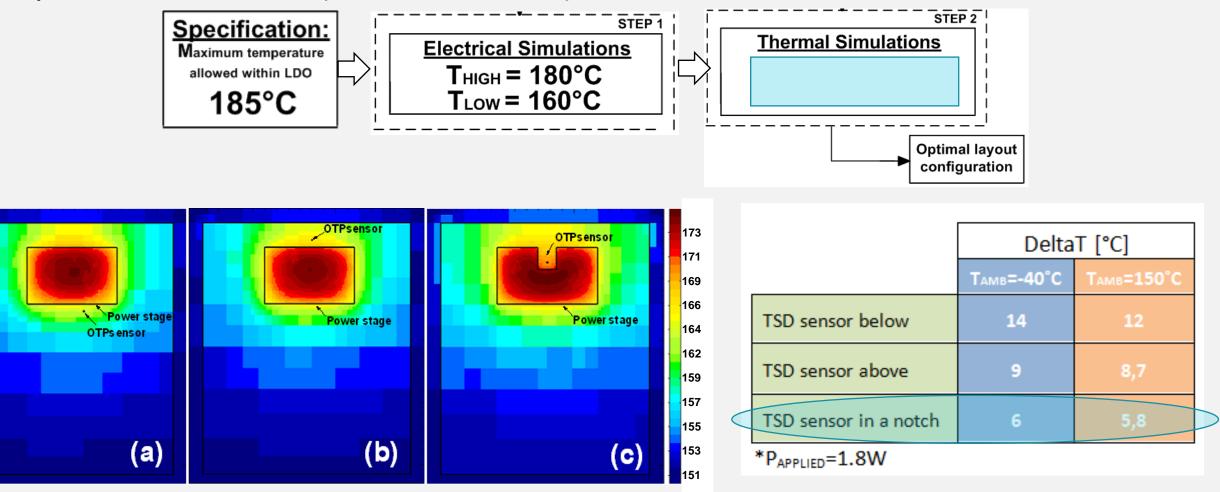

Design Example

Steps 1 & 2: Electrical-only and Thermal-only sime

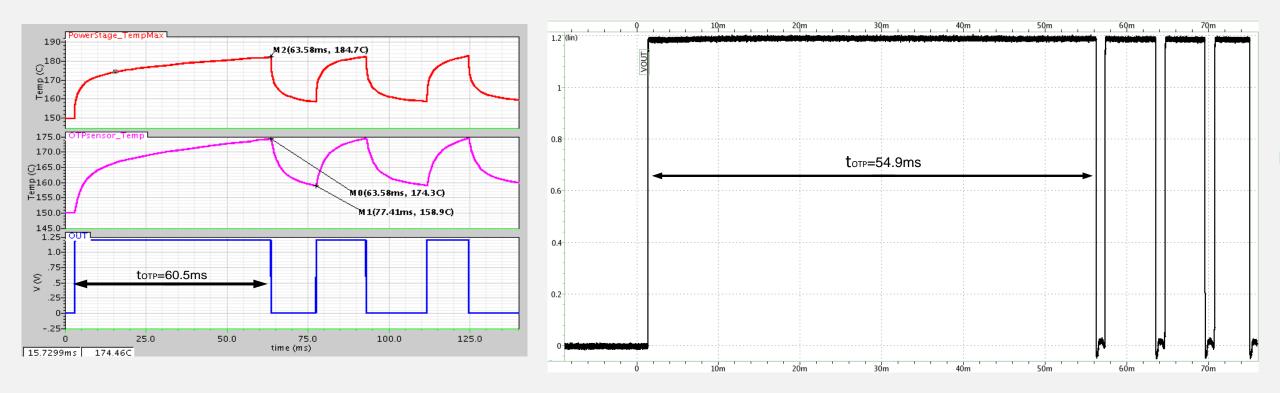

#### Step 3: Electro-Thermal sims

#### Measurement results:

> Good agreement between the measurements and the electro-thermal simulations results regarding the time until the OTP event occurs ( $t_{OTP}$ ): 59.5 ms and 60.5 ms

# Summary and Conclusions

#### > Systematic design (as opposed to simulation driven design):

- mathematical analysis => understanding of design constraints and trade-offs

- sizing strategy => 1<sup>st</sup> iteration "design-by-hand" close-to-spec & help next iteration(s)

- Optimization tools used only after a few "design-by-hand" iterations & driven by designer

#### Analog designers need new tools and design methodologies

- Electro-thermal simulators crucial for robust design

- Mechanical phenomena should also be considered, especially for duty-cycled operation

#### > Circuit design should be an important part of the development strategy for microelectronics

- Key part of the eco-system, essential for taking full advantage of new technologies

- Experience & talent are essential in IC design => relocating jobs less likely than in software development

- Easier to start-up and to scale-up successful design teams than technology-focused research

- Romanian Universities have experienced teachers, as well as the design tools and access to silicon fabs. the students need in order to acquire the skills and abilities essential for IC design